AI助力芯片设计效率变革,Jeff Dean带领提出最新方案

发布时间:2024-05-16 14:16:43 浏览量:228次

设计一款高端芯片有多难?想象一下要将上百亿个晶体管集成到指甲盖大小的区域上,还要进行各类功能区域规划,这是一项多么微观且浩瀚的工程。

如今,最基本的芯片晶体管部件都是微米、纳米级尺度,如何铺设和利用这几百亿个晶体管,如何通过模块设计组合迸发出一款芯片的极致性能,如何满足日益增长的终端需求,这是如今芯片设计工程师们面临的严苛挑战,而且如此复杂的设计,不能有纰漏缺陷。

现在,随着 AI 技术深入到芯片设计领域,一场效率革命可能要再次席卷而来。

来自由 Jeff Dean 领衔的谷歌大脑团队以及斯坦福大学计算机科学系的科学家们,在一项联合研究中证明,一种基于深度强化学习的芯片布局规划方法,能够生成可行的芯片设计方案。

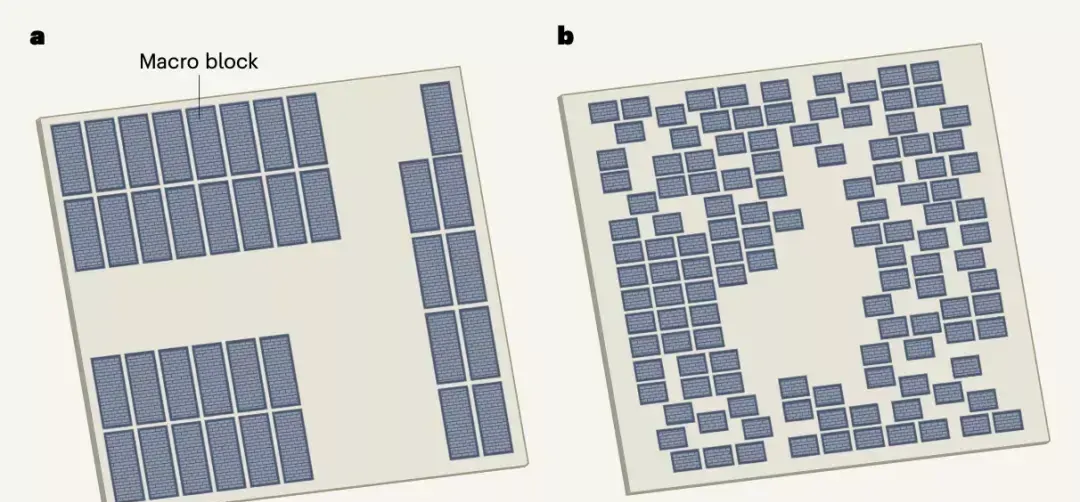

图|人类设计的微芯片平面图与机器学习系统设计的不同(来源:Nature)

在不到 6 小时的时间内,由该方法自动生成的芯片平面图在所有关键指标上都优于或与人类专家生成的设计图效果相当,而人类工程师往往需要数月的紧张努力才能达到如此效果。

(来源:Nature)

芯片设计工程师的AI助理

事实上,科学家们一直在探索让芯片设计过程更高效的路径。

重大的进步出现在 1980 年代,电子设计自动化(EDA)技术诞生,开发人员能将整个设计过程自动化,利用计算机辅助设计(CAD)软件,完成超大规模集成电路(VLSI)的功能设计、综合、验证、物理设计等复杂流程,EDA 的不断完善架起了芯片设计与制造之间的桥梁。

尽管已经经过了 50 年的相关研究,但芯片布局规划仍无法实现自动化,依然需要物理设计工程师数月精心布置才能完成可制造的芯片布局。

据论文描述,如今这种方法已经被用于下一代 Google 张量处理单元(TPU)加速器的产品中,有望为今后的每一代计算机芯片迭代节省数千小时的人力。

设计域的自适应策略

为了解决这类复杂的芯片布局规划问题,研究人员开发了一种强化学习方法,该方法能够跨芯片进行推广,使芯片设计师能够得到AI的协助,且这个AI助理的“经验”比任何人都丰富。

研究人员相信,这种AI布局优化方法策略可以应用于芯片设计以外更广泛的有效布局问题。

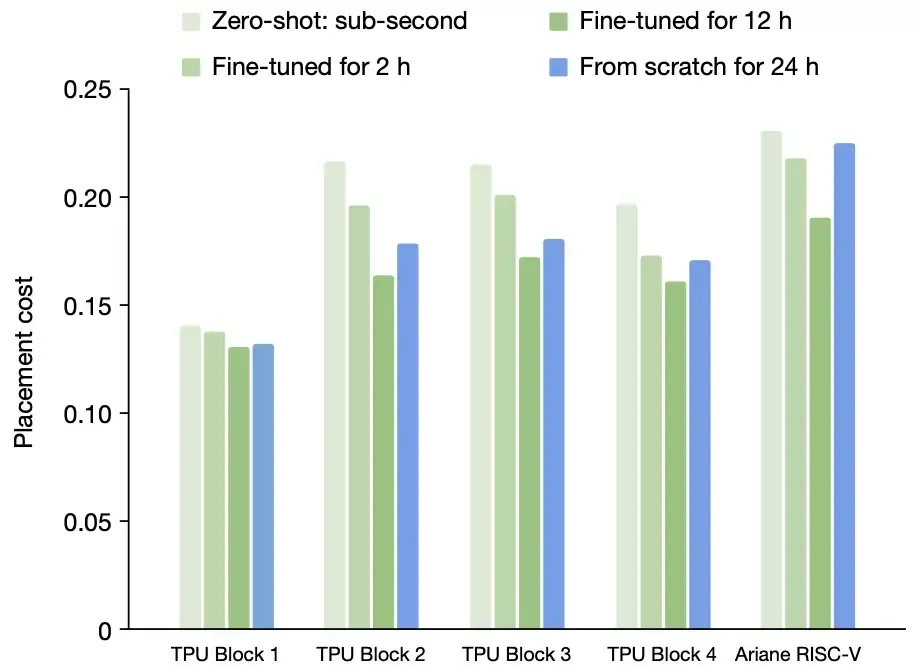

从无到有的训练与不同时间量的微调,从表中可以看出,预先训练的策略网络始终优于从无到有训练的策略网络,证明了从离线训练数据中学习的有效性(来源:该论文)

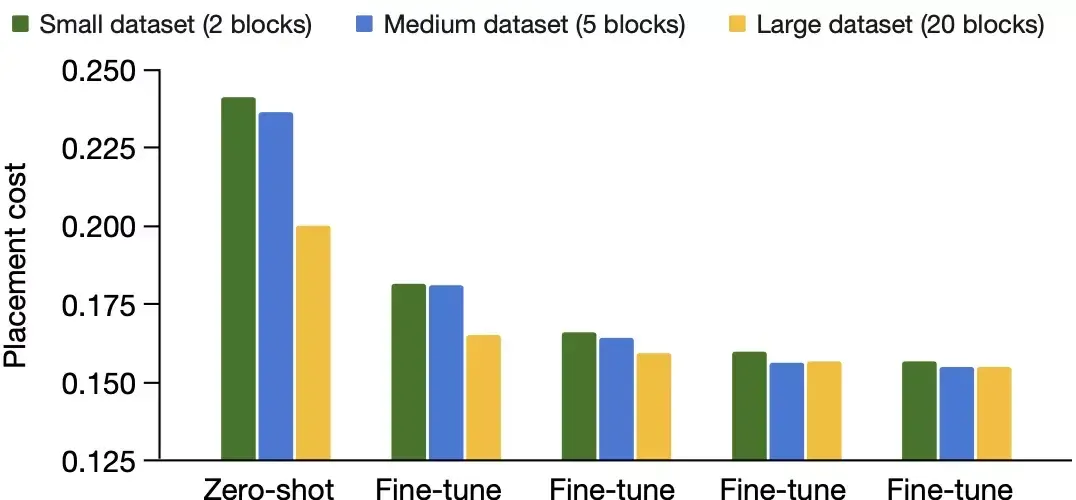

训练前数据集大小的影响(来源:该论文)

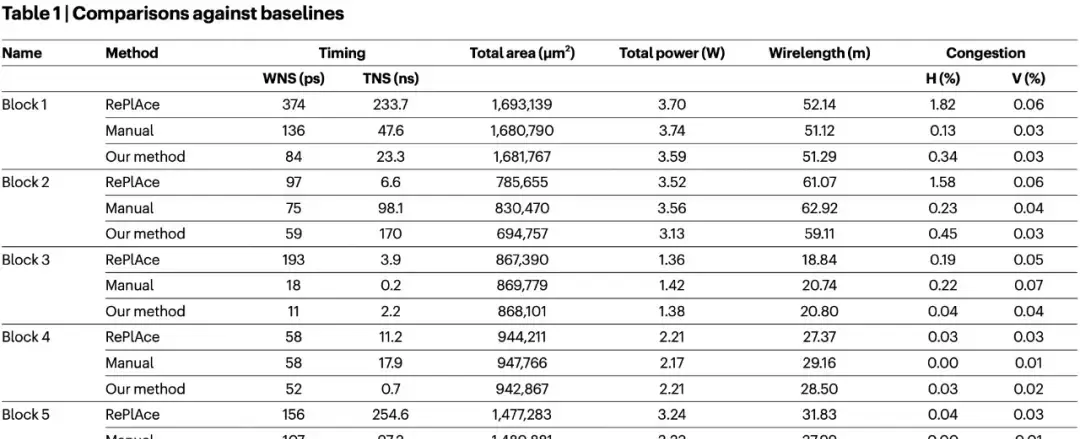

与基线的比较,AI布局芯片的方法与最先进的方法,以及使用行业标准EDA工具手动放置进行比较。对于本表中的所有指标,越低越好(来源:该论文)

结果证明,利用AI进行芯片设计布局是有效的,不仅能生成高质量的模块放置方案,也能满足实际设计标准要求,优于或不亚于人类专家手动放置的效果。

加利福尼亚大学圣迭戈分校电气与计算机工程系专家 Andrew B. Kahng对这项成果评论称,对于芯片设计和设计自动化领域的长期实践者来说,这项研究成果确实很神奇。

最重要的启示可能是,该技术方案已经被纳入我公司下一代AI处理器的芯片设计中,这意味着这种解决方案足够好、足够成熟,可以在昂贵、尖端的硅片上批量复制,未来可以期望半导体行业加倍关注此类相关工作。

热门资讯

-

1. 华为手机神奇“AI修图”功能,一键消除衣服!原图变身大V领深V!

最近华为手机Pura70推出的“AI修图”功能引发热议,通过简单操作可以让照片中的人物换装。想了解更多这款神奇功能的使用方法吗?点击查看!

-

近年来,人工智能逐渐走入公众视野,其中的AI图像生成技术尤为引人注目。只需在特定软件中输入关键词描述语以及上传参考图就能智能高效生成符合要求的...

-

想将照片变成漫画效果?这篇文章分享了4个方法,包括Photoshop、聪明灵犀、VanceAI Toongineer、醒图,简单操作就能实现,快来尝试一下吧!

-

4. 一款免费无限制的AI视频生成工具火了!国内无障碍访问!附教程

人人都可以动手制作AI视频! 打开网址https://pixverse.ai/,用邮箱注册后,点击右上角Create,就可以开始创作了。 PixVerse目前有文案生成视频,和图片生...

-

以下是一些免费的AI视频制作网站或工具,帮助您制作各种类型的视频。 1. Lumen5:Lumen5是一个基于AI的视频制作工具,可将文本转换为视频。 用户可以使...

-

6. 零基础10分钟生成漫画,教大家如何用AI生成自己的漫画

接下来,我将亲自引导你,使用AI工具,创作一本既有趣又能带来盈利的漫画。我们将一起探索如何利用这个工具,发挥你的创意,制作出令人惊叹的漫画作品。让...

-

就能快速生成一幅极具艺术效果的作品,让现实中不懂绘画的人也能参与其中创作!真的超赞哒~趣趣分享几款超厉害的AI绘画软件,提供详细操作!有需要的快来...

-

8. AI视频制作神器Viggle:让静态人物动起来,创意无限!

Viggle AI是一款免费制作视频的AI工具,能让静态人物图片动起来,快来了解Viggle AI的功能和优势吧!

-

9. 10个建筑AI工具,从设计到施工全覆盖!肯定有你从来没听过的

讲述了建筑业比较著名的AI公司小库科技做出的探索,在这儿就不多说了。今天,我们试着在规划设计、建筑方案设计、住宅设计、管道设计、出渲染图、3D扫...

-

10. Logo Diffusion——基于sd绘画模型的AI LOGO 生成器

这下LOGO设计彻底不用求人了。接下来详细演示一遍操作流程首先进入Logo D... 想学习更多AI技能,比如说关于怎么样利用AI来提高生产效率、还能做什么AI...

最新文章

火星网校

火星网校